* On your first PCB Assembly order!

* Up to $300 discount

C - A L L E Y

C - A L L E Y

About Us | Events | Company Structure | Management Staff Structure | Market Focus | Company Certification | Our Services

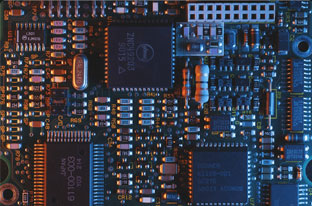

How can a company expect to apply advanced PCB technologies and still meet productivity and time-to-market goals? Part of the answer is to ensure that the tools they are using have kept up with the challenges of these advanced technologies. Here’s some of the capabilities required in today’s tools.

High-Density, High Pin-Count BGAs

Today’s IC packages have more pins at smaller spacing. This is great for squeezing more functionality into smaller spaces, but the problem is routing from those dense BGAs to the rest of the PCB. This is usually done in two steps. The first is to connect from the surface BGA pads into the inner layers of the PCB (the fanout). The second is to connect from those inner-layer vias to the rest of the components on the PCB. This process can take a layout designer days of interactive routing if handled manually.

Some design tools can automate this process, developing the interconnect in minutes versus days. The first step is the fanout. This can be done using either HDI/Microvia layers or through-vias. The first step enables the user to define a fanout pattern. The actual fanout routing takes seconds with an automated function.

Example of C-alley will automated fanout using a template and HDI/Microvias.

The second step is to connect from this fanout to the rest of the board. There are two ways to do this. The first is to apply a ‘North-South-East-West’ pattern, which uses the layers and escapes to the nearest edge of the BGA. The second is a ‘layer-biased’ approach in which the breakouts go in the direction of the interconnect and are biased to the layer direction.

Performance: Increases in IC density and performance have affected PCB design. The first effect is the increase in the proportion of high-speed interconnects that must be finely tuned for delay, crosstalk and signal integrity. Such PCBs need to be simulated and analyzed to ensure that the critical signal corner cases meet spec at extreme temperature and manufacturing tolerances.

C-alley considering that advanced design systems enable engineers to pre-analyze the high-speed net classes and set up constraints for those interconnects. These constraints are carried through the rest of the design system and available to the layout and the post-layout analysis steps. During layout, whether the CAD design is performing interactive or automatic routing, the constraints are followed to meet the length (delay), parallelism (crosstalk) and tolerance (matching) specs. For boards with many constrained interconnects, this automation provides the productivity and accuracy to produce a correct board the first time, on time.

The second high-performance issue is thermal management. If the junction temperature of an IC goes above its specified level, the IC suffers both reduced performance and long-term reliability issues. Solving the heat management problem is a multi-level task .

C-ALLEY sincerely wish our shares may of any help to your business . if you have any question welcome send us !

Please send Email to kspcba@c-alley.com or call us through +86 13828766801 Or submit your inquiry by online form. Please fill out below form and attach your manufacturing files( PCB Gerber files and BOM List) if need quotation. We will contact you shortly.

+86 13828766801

+86 13828766801 kspcba@c-alley.com

kspcba@c-alley.com https://www.kingshengpcba.com/

https://www.kingshengpcba.com/ 2/F, Building 6, Tangtou 3rd Industrial Zone, Tangtou Community, Shiyan Town, Baoan District, Shenzhen, China, 518108

2/F, Building 6, Tangtou 3rd Industrial Zone, Tangtou Community, Shiyan Town, Baoan District, Shenzhen, China, 518108